Detailed Description

Hardware Overview

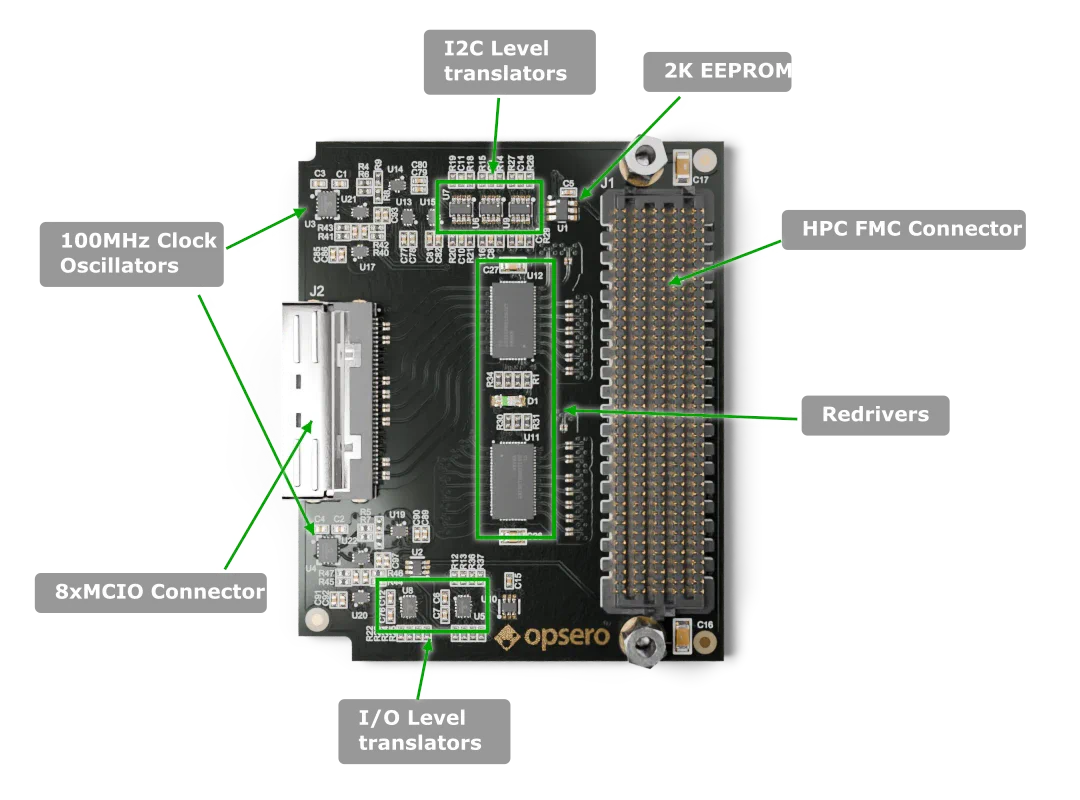

The figure below illustrates the various hardware components that are located on the top-side of the MCIO PCIe FMC.

The main components on the top-side of the mezzanine card are:

- 8xMCIO Connector

- High Pin Count FMC Connector

- 2K EEPROM

- 2x 100MHz Clock oscillators

- 2x PCIe Redrivers

- Level translators

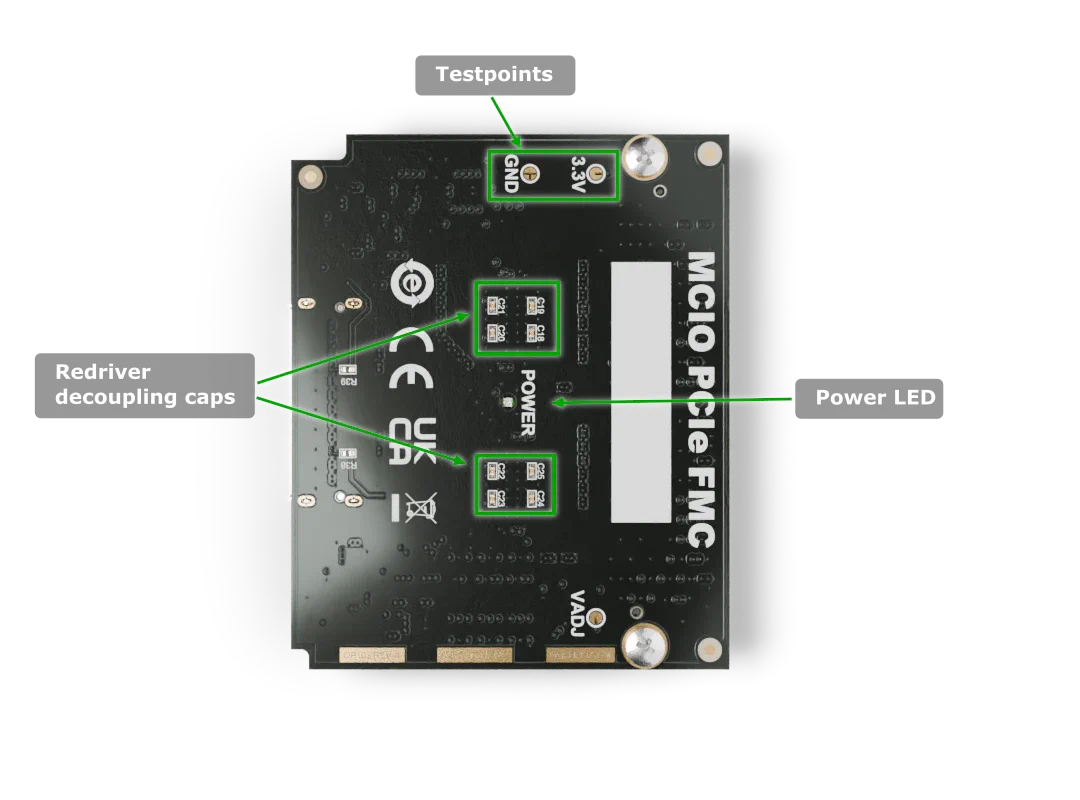

The figure below illustrates the various hardware components that are located on the bottom-side of the mezzanine card.

The main components on the bottom-side of the mezzanine card are:

- FMC Power indicator LED

- Redriver decoupling capacitors

- Test points for power supplies

MCIO connector

The Amphenol ICC, 8xMCIO Connector, G97R22312HR , has 8 gigabit transceiver lanes that can be used as two 4-lane links, or as a single 8-lane link. Although the connector and mezzanine card are optimized for PCIe links, they can be used with other serial link standards.

The MCIO connector carries two types of signals: transceiver lanes and sideband signals. Both are organized into two independent channels, A and B.

The transceiver lanes handle high-speed serial data and are labelled PER (receive) and PET (transmit). Lanes 0 through 3 belong to channel A, and lanes 4 through 7 belong to channel B.

Each channel also has its own set of sideband signals, identified by an A or B suffix:

- REFCLKA/B_P/N — Reference clock

- PERSTA/B_N — PCIe reset

- PRSNTA/B_N — Device present detect

- 2WA/B_SCL and 2WA/B_SDA — I2C clock and data

- BP_TYPEA/B — Backplane type (not used on this mezzanine card)

- CWAKEA/B_N — Clock wake (not used on this mezzanine card)

The pinout of the sideband signals on the MCIO connector depends on whether it is being used in host or device mode and is determined by a logic signal on the FMC interface. This allows the same connector to operate in both host mode and device mode, with the carrier board’s FPGA selecting the desired mode on configuration.

The pinout of the MCIO connector in each mode is shown in the table below:

| Pin # | Host mode | Device mode | Pin # | Host mode | Device mode |

|---|---|---|---|---|---|

| A1 | GND | GND | B1 | GND | GND |

| A2 | PER_0P | PER_0P | B2 | PET_0P | PET_0P |

| A3 | PER_0N | PER_0N | B3 | PET_0N | PET_0N |

| A4 | GND | GND | B4 | GND | GND |

| A5 | PER_1P | PER_1P | B5 | PET_1P | PET_1P |

| A6 | PER_1N | PER_1N | B6 | PET_1N | PET_1N |

| A7 | GND | GND | B7 | GND | GND |

| A8 | BP_TYPEA | 2WA_SCL | B8 | 2WA_SCL | BP_TYPEA |

| A9 | CWAKEA_N | 2WA_SDA | B9 | 2WA_SDA | CWAKEA_N |

| A10 | GND | GND | B10 | GND | GND |

| A11 | REFCLKA_P | PERSTA_N | B11 | PERSTA_N | REFCLKA_P |

| A12 | REFCLKA_N | PRSNTA_N | B12 | PRSNTA_N | REFCLKA_N |

| A13 | GND | GND | B13 | GND | GND |

| A14 | PER_2P | PER_2P | B14 | PET_2P | PET_2P |

| A15 | PER_2N | PER_2N | B15 | PET_2N | PET_2N |

| A16 | GND | GND | B16 | GND | GND |

| A17 | PER_3P | PER_3P | B17 | PET_3P | PET_3P |

| A18 | PER_3N | PER_3N | B18 | PET_3N | PET_3N |

| A19 | GND | GND | B19 | GND | GND |

| A20 | PER_4P | PER_4P | B20 | PET_4P | PET_4P |

| A21 | PER_4N | PER_4N | B21 | PET_4N | PET_4N |

| A22 | GND | GND | B22 | GND | GND |

| A23 | PER_5P | PER_5P | B23 | PET_5P | PET_5P |

| A24 | PER_5N | PER_5N | B24 | PET_5N | PET_5N |

| A25 | GND | GND | B25 | GND | GND |

| A26 | BP_TYPEB | 2WB_SCL | B26 | 2WB_SCL | BP_TYPEB |

| A27 | CWAKEB_N | 2WB_SDA | B27 | 2WB_SDA | CWAKEB_N |

| A28 | GND | GND | B28 | GND | GND |

| A29 | REFCLKB_P | PERSTB_N | B29 | PERSTB_N | REFCLKB_P |

| A30 | REFCLKB_N | PRSNTB_N | B30 | PRSNTB_N | REFCLKB_N |

| A31 | GND | GND | B31 | GND | GND |

| A32 | PER_6P | PER_6P | B32 | PET_6P | PET_6P |

| A33 | PER_6N | PER_6N | B33 | PET_6N | PET_6N |

| A34 | GND | GND | B34 | GND | GND |

| A35 | PER_7P | PER_7P | B35 | PET_7P | PET_7P |

| A36 | PER_7N | PER_7N | B36 | PET_7N | PET_7N |

| A37 | GND | GND | B37 | GND | GND |

The MCIO connector organizes its pins into two rows: the A-side and the B-side. The high-speed differential pairs are arranged such that the receive pairs (PER) are on the A-side and the transmit pairs (PET) are on the B-side. These assignments are consistent regardless of whether the connector is operating in host or device mode — the data lanes themselves do not change function between modes.

When an MCIO cable connects two devices, it crosses the A-side of one connector to the B-side of the other, and vice versa. This crossover is what establishes the correct TX-to-RX routing required by PCIe: the transmit pairs (PET) from one end of the cable arrive at the receive pairs (PER) of the other end, and the same applies in the opposite direction. No additional switching of the high-speed data lanes is needed.

However, the cable crossover also affects the sideband signals that occupy specific pin positions alongside the data lanes. In a standard PCIe connection, certain sideband signals are outputs on the host side and inputs on the device side. For example, the reference clock (REFCLK) is provided by the host, while the reset signal (PERST_N) is driven by the host toward the device. The presence detect (PRSNT_N) signal, on the other hand, is driven by the device toward the host. Because the cable swaps A-side and B-side pins, these sideband signals naturally land on the correct pins at each end — but only if the connector is wired for the appropriate mode.

Since the MCIO PCIe FMC supports both host and device modes through the same connector, the sideband pins must serve a dual purpose. In host mode, the A-side sideband pins carry host-sourced signals such as REFCLK and the B-side carries device-sourced signals such as PERST_N and PRSNT_N. In device mode, these roles are reversed to match what the remote host expects to see at the other end of the cable. The mezzanine card manages this by using multiplexers on the sideband pins, controlled by a mode selection logic signal on the FMC interface, which routes the correct signals to the correct pins based on the selected operating mode.

High-speed Switches

The mezzanine card uses several high-speed switches ( TI, 480Mbps MUX/DEMUX Switch, TMUXHS221NKGR ) to allow the sideband signals to be switched between host and device mode. Each switch determines the purpose of a single sideband pair. For example, pair A11/A12 connects to clock oscillator output in host mode, while in device mode it connects to PERSTA_N and CPRSNTA_N. The SEL input of all switches is connected to the HOST_MODE_N signal that is driven by the FPGA.

EEPROM

The EEPROM ( Microchip, 2Kbit EEPROM, 34AA02T-I/OT ) stores IPMI FRU data that can be read by the carrier board and contains the following information:

- Manufacturer name (Opsero Electronic Design Inc.)

- Product name

- Product part number

- Serial number

- Power supply requirements

The FRU data is read by some carrier boards to determine the correct VADJ voltage to apply to the mezzanine card. All Opsero FMC products have their EEPROMs programmed with valid FRU data to allow these carrier boards to correctly power them.

High Pin Count FMC Connector

The MCIO PCIe FMC has a high pin count (HPC) FMC (FPGA Mezzanine Card) connector for interfacing with an FPGA or SoC development board. The part number of this connector is Samtec, High pin count FMC connector, Module side, ASP-134488-01 . This HPC FMC connector can be mated with LPC, HPC or FMC+ carrier connectors.

The pinout of this connector conforms to the VITA 57.1 FPGA Mezzanine Card Standard (for more information, see Pin configuration. For more information on the FMC connector and the VITA 57.1 standard, see the Samtec page on VITA 57.1 .

I/O Interfaces

The FMC connector provides power to the MCIO PCIe FMC and also presents the following I/O signals to the FPGA fabric of the development board:

- 8x gigabit transceivers

- PERSTA_N and PERSTB_N active-low reset signals for channel A and B (driven by FPGA in host mode, driven by MCIO in device mode)

- PRSNTA_N and PRSNTB_N active-low present signals for channel A and B (driven by MCIO in host mode, driven by FPGA in device mode)

- SBA_DISABLE and SBB_DISABLE active-high signals to disable sidebands for channel A and B

- HOST_MODE_N for selecting between host and device modes

- LOCAL_CLKS_N for selecting the FPGA clock source between local clock and MCIO clock (in device mode only)

- 2x LVDS 100MHz reference clocks

- I2C for FMC EEPROM

- I2C for MCIO Channel-A

- I2C for MCIO Channel-B

- I2C for Redriver configuration

Host Mode

The figure below illustrates the main connections to the FMC connector in host mode (HOST_MODE_N = LOW, LOCAL_CLKS_N = LOW). For clarity we have left out the switches and level translators from the diagram.

Device Mode

The figure below illustrates the main connections to the FMC connector in device mode (HOST_MODE_N = HIGH, LOCAL_CLKS_N = HIGH). For clarity we have left out the switches and level translators from the diagram.

Gigabit Transceivers

The 8x PCIe lanes of the MCIO connector are routed to FMC pins that are dedicated to gigabit transceivers. The first four lanes are referred to as channel A, while the second four lanes are referred to as channel B (not to be confused with row-A and row-B of the MCIO connector). The connections are shown in the tables below.

MCIO Channel A

| Direction | PCIe lane | FMC Pin | FMC name | Net name |

|---|---|---|---|---|

| MCIO-to-FPGA | 0 | C6/C7 | DP0_M2C_P/N | PERA_0_P/N |

| 1 | A2/A3 | DP1_M2C_P/N | PERA_1_P/N | |

| 2 | A6/A7 | DP2_M2C_P/N | PERA_2_P/N | |

| 3 | A10/A11 | DP3_M2C_P/N | PERA_3_P/N | |

| FPGA-to-MCIO | 0 | C2/C3 | DP0_C2M_P/N | PETA_0_P/N |

| 1 | A22/A23 | DP1_C2M_P/N | PETA_1_P/N | |

| 2 | A26/A27 | DP2_C2M_P/N | PETA_2_P/N | |

| 3 | A30/A31 | DP3_C2M_P/N | PETA_3_P/N |

MCIO Channel B

| Direction | PCIe lane | FMC Pin | FMC name | Net name |

|---|---|---|---|---|

| MCIO-to-FPGA | 0 | A14/A15 | DP4_M2C_P/N | PERB_0_P/N |

| 1 | A18/A19 | DP5_M2C_P/N | PERB_1_P/N | |

| 2 | B16/B17 | DP6_M2C_P/N | PERB_2_P/N | |

| 3 | B12/B13 | DP7_M2C_P/N | PERB_3_P/N | |

| FPGA-to-MCIO | 0 | A34/A35 | DP4_C2M_P/N | PETB_0_P/N |

| 1 | A38/A39 | DP5_C2M_P/N | PETB_1_P/N | |

| 2 | B36/B37 | DP6_C2M_P/N | PETB_2_P/N | |

| 3 | B32/B33 | DP7_C2M_P/N | PETB_3_P/N |

Reference clocks

The mezzanine card has two clock oscillators ( MicroChip, 2x Output PCIe Clock Generator, DSC557-0334FI1 ), one for each MCIO channel. Each clock oscillator generates two synchronous 100MHz clocks; one LVDS and the other HCSL. The LVDS clocks are intended for driving the GT ref clocks, while the HCSL clocks are intended for the MCIO.

The GT ref clocks can be driven either by the on-board clock oscillators (locally) or by the remote clocks supplied by the connected MCIO host (when used in device mode). The clocks are selected by driving the LOCAL_CLKS_N signal (see below for more information on this signal).

| Synchronous to | FMC Pin | FMC name | Net name |

|---|---|---|---|

| MCIO Channel A | D4/D5 | GBTCLK0_M2C_P/N | CLKA_F_P/N |

| MCIO Channel B | B20/B21 | GBTCLK1_M2C_P/N | CLKB_F_P/N |

When used in host mode, the GT ref clocks must be driven with the local clocks (LOCAL_CLKS_N = LOW). When used in device mode, it is typical to use the remote clock provided by the connected MCIO host to drive the GT ref clocks (LOCAL_CLKS_N = HIGH).

PERST_N

The PERSTA_N and PERSTB_N signals are active-low reset signals for MCIO channels A and B respectively. They are driven by the FPGA in host mode, and driven by the MCIO link partner in device mode. Level translators convert these signals from VADJ levels (FPGA side) to 3.3V levels (MCIO side). The function of these signals is shown in the table below:

| PERSTA/B_N | Function |

|---|---|

| 0 (LOW) | MCIO device in reset |

| 1 (HIGH) | MCIO device operational |

Pull-up resistors are tied to these signals on the mezzanine card on the 3.3V side so that they are not left floating if in device mode and the MCIO cable is disconnected.

Pull-up resistors are tied to these signals on the mezzanine card on the VADJ side so that they are not left floating if in host mode and the pins have not been connected in the FPGA design.

PRSNT_N

The PRSNTA_N and PRSNTB_N signals are active-low signals driven by the MCIO device to indicate presence. In host mode, the FPGA can read this signal to determine if an MCIO device is connected. In device mode, the FPGA should drive this signal LOW to indicate its presence to the MCIO host. The functionality of these signals is described in the table below:

| PEDETA/B_N | Function |

|---|---|

| 0 (LOW) | Device present |

| 1 (HIGH) | Device NOT present |

Pull-up resistors are tied to these signals on the mezzanine card so that they default to HIGH when in host mode and the MCIO cable is disconnected.

Pull-down resistors are tied to these signals on the mezzanine card on the VADJ side so that they are not left floating if in device mode and the pins have not been connected in the FPGA design.

HOST_MODE_N

The HOST_MODE_N signal is an active-low signal that determines whether the mezzanine card is in host or device mode. When driven LOW, the mezzanine card is configured for host mode. When driven HIGH, the mezzanine card is configured for device mode.

| HOST_MODE_N | Function |

|---|---|

| 0 (LOW) | Host mode |

| 1 (HIGH) | Device mode |

LOCAL_CLKS_N

The LOCAL_CLKS_N signal is an active-low signal that determines whether the gigabit transceiver reference clocks will be driven by local or remote clock sources. When used in device mode, we can choose to drive the GT ref clocks with the local clocks generated by the mezzanine card’s 100MHz clock oscillators, or with the remote clocks provided by the connected MCIO host.

When driven LOW, the local clock oscillators will drive the GT reference clock inputs. When driven HIGH, the MCIO host provided clocks will drive the GT reference clock inputs. Note that when used in host mode, the local clock oscillators should always be used as the GT reference clocks and LOCAL_CLK_N should always be driven LOW.

| LOCAL_CLKS_N | Function |

|---|---|

| 0 (LOW) | Local clocks drive GT refclks |

| 1 (HIGH) | Remote clocks (from MCIO host) drive GT refclks |

SBx_DISABLE

The SBA_DISABLE and SBB_DISABLE signals can be used to disable the sideband signals of MCIO channel A and B respectively. The main purpose of this feature is to allow support of the Open Compute Project M-XIO standard. For most other applications of this mezzanine card, both sideband channels should be enabled.

The MCIOx8 connector on the mezzanine card is wired for SFF-9402 standard by default. To make the connector compatible with OCP M-XIO standard, albeit without 3P3VAUX_MGMT, USB or FLEXIO support, drive the SBB_DISABLE signal HIGH to disconnect the sideband B signals.

Disabling the sideband signals of a channel leaves those MCIO pins in a high-impedance state.

| SBA/B_DISABLE | Function |

|---|---|

| 0 (LOW) | Enable sideband signals |

| 1 (HIGH) | Disable sideband signals |

Power Supplies

All power required by the MCIO PCIe FMC is supplied by the development board through the FMC connector:

- +12VDC (not used by the mezzanine card)

- +3.3VDC

- +3.3VAUX (for powering EEPROM only)

- VADJ: +1.2VDC-3.3VDC

All devices on the mezzanine card are powered by the 3.3VDC supply of the FMC connector. The +12VDC supply of the FMC connector is not used by this mezzanine card. The VADJ supply does not power any devices but is used to provide reference to the level translators.

The 3.3VDC Supply

The 3.3VDC supply provides power for the redrivers, the clock oscillators, the switches, the inverters, the EEPROM and the level translators.

VADJ Supply

The adjustable voltage supply (VADJ), is the I/O voltage that is supplied by all standard FMC carriers. The MCIO PCIe FMC can accept any VADJ voltage in the range of 1.2V to 3.3V. The mezzanine card has an onboard FRU EEPROM that specifies acceptance of any VADJ voltage within the range 1.2V to 3.3V (see note below). All carriers with a power management system will read this EEPROM on power-up and apply a voltage in the range specified by the EEPROM. Note that some development boards require the VADJ voltage to be configured by a DIP switch or jumper placement, in which case we suggest that it be set to 1.8V.

Power LED and testpoints

A single green LED on the mezzanine card is used to indicate when the required power supplies are active. The location of this LED can be seen in the labelled bottom view of the board above. The LED indicates when the FMC’s 12VDC, 3.3VDC and VADJ voltages are active.

To aid hardware debug, test points are accessible on the bottom side of the mezzanine card for the 3.3V and VADJ power supplies of the MCIO PCIe FMC.